Schaltungsentwicklung für Neuromorphic Computing | Über einen vielversprechenden Ansatz für neue Rechentechnologien

Konventionelle Computersysteme verarbeiten Daten seriell und trennen strikt zwischen Rechnen und Speichern. Neuromorphes Computing hingegen orientiert sich am Aufbau biologischer Gehirne, in denen Informationen parallel über komplexe Netzwerke aus Neuronen und Synapsen verarbeitet werden. Damit dieses Konzept in die mikroelektronische Anwendung übertragen werden kann, ist eine ganzheitliche Herangehensweise und enge Abstimmung zwischen Hardware- und Software-Design nötig. Ferdinand Pscheidl, wissenschaftlicher Mitarbeiter am Fraunhofer EMFT, beschäftigt sich in seiner Arbeit mit der Entwicklung dieser Hardware. Im Interview erklärt er, welche Potenziale neuromorphes Computing bietet, welche Herausforderungen bestehen und für welche Anwendungsfelder die Technologie besonders vielversprechend ist.

Herr Pscheidl, Sie arbeiten am Fraunhofer EMFT in der Gruppe für Circuit Design und beschäftigen sich insbesondere mit der Schaltungsentwicklung für neuromorphes Computing. Können Sie das genauer erklären?

Vereinfacht gesagt, versuchen wir, Systeme inspiriert von menschlichen bzw. biologischen Gehirnen zu bauen. Mit diesem Ansatz brechen wir die Grenze zwischen Rechnen und Speichern, und bringen diese beiden Funktionen näher auf einem Chip zusammen, was eine parallele und energieeffiziente Datenverarbeitung ermöglicht. Ein wichtiger Aspekt dabei ist, dass nicht nur der Wert (1 oder 0) eines Signals zählt, sondern auch der Zeitpunkt, zu dem es auftritt. Diese zeitliche Information nutzen wir gezielt – etwa in sogenannten Spiking Neural Networks (SNN), auf die wir uns in unserer Arbeit fokussieren. Ein großer Vorteil ist, dass die sogenannte Sparcity (auf Deutsch: Spärlichkeit) der Informationen ausgenutzt werden kann. Das heißt, es wird nur dann gerechnet, wenn tatsächlich relevante Signale auftreten. So wird die Effizienz des Systems erhöht.

Seit wann beschäftigen sich Forschende in der Mikroelektronik mit neuromorphem Computing? Und warum wurde der Ansatz lange nicht weiterverfolgt?

Der Ansatz lässt sich bereits 40 Jahre zurückverfolgen. Carver Mead, der Pionier für VLSI-Design (Very-Large-Scale Integration), war der Erste, der erkannt hat, dass sich ein Transistor ähnlich zu Synapsen und Neuronen in der Biologie verhält. Die Frage, die er sich damals schon stellte, war also: Wie kann diese biologische Funktionsweise in der Mikroelektronik umgesetzt werden?

Nun ist es so, dass Chip- und Softwareentwicklung für neuromorphe Prozessoren ohne moderne konventionelle Prozessoren und Grafikkarten kaum vorstellbar ist. Das heißt, die Entwicklung auf diesem Gebiet ist deutlich anspruchsvoller als die Designs, die zuvor für klassische Mikroprozessoren und deren Speicher benötigt wurden. Auch wirtschaftlich war das Thema lange unattraktiv. Die Aussicht, damit in kurzer Zeit viel Geld zu verdienen, war gering. Zumal davon ausgegangen wurde, dass mit den herkömmlichen Mikroprozessoren und Speichern für Mikroprozessoren noch lange viel Geld zu verdienen ist. Wir sehen jetzt aber, dass dieser Trend an sein Ende kommt.

Sie beziehen sich auf Moore’s Law?

Genau. Es hat sich früh abgezeichnet, dass irgendwo bei 2 Nanometer die Grenze der Integrationsdichte erreicht sein wird. Aber das Businessmodell war lukrativ: Jahrzehntelang konnte die gleiche Art von Chips hergestellt werden und durch das exponentielle Wachstum der Anzahl der Transistoren auf einem Chip wurden die Chips auch immer besser. Wir haben aber mittlerweile die Grenze erreicht, sodass das Interesse an alternativen Rechenarchitekturen in den letzten fünf bis zehn Jahren deutlich zugenommen hat. Davon profitieren nicht nur wir im neuromorphen Bereich, sondern auch die Themen Quantencomputing, Photonic Computing oder Heterointegration.

Der Trend geht zunehmend dahin, anwendungsspezifische Lösungen zu entwickeln, anstatt weiterhin auf allgemeine Systeme wie beispielsweise CPUs (Core Processing Unit) zu setzen. Für uns bedeutet das: Wir wollen Hardware bauen, die speziell für Spiking Neural Networks funktioniert. Denn ein SNN wird so designt und trainiert, dass es spezifisch für eine Anwendung geeignet ist.

Für neuromorphes Computing braucht es aufeinander abgestimmte Hard- und Software. Werfen wir zunächst einen Blick auf die bereits angesprochene Hardware. Was zeichnet einen neuromorphen Chip gegenüber anderen Halbleiterchips aus?

Ein SNN arbeitet ganz anders als ein klassisches künstliches neuronales Netz. Beim SNN laufen die Daten als zeitlich verteilte Signale – sogenannte Spikes oder Pulse – durch das Netzwerk. Diese Signale können über einen längeren Zeitraum hinweg ständig eintreffen.

Wird ein SNN auf herkömmlicher Hardware wie Prozessoren oder Grafikkarten simuliert, muss der Zustand des gesamten Netzwerks bei jedem einzelnen Zeitschritt neu berechnet werden. Bei einer Simulation über eine Sekunde mit einer Auflösung von 100 Megahertz (100 Millionen Zeitschritten pro Sekunde) bedeutet das 100 Millionen Berechnungen. Das ist extrem rechenaufwendig und langsam.

Neuromorphe Chips lösen dieses Problem, weil sie ereignisbasiert, massiv parallel und in Echtzeit arbeiten. Das heißt, die Simulation der Zeit ist entweder durch getaktete Zeitschritte fest in der Hardwarearchitektur verankert oder einfach durch das zeitliche Verhalten von asynchronen Schaltungen bestimmt. Dadurch sind sie viel effizienter und schneller bei der Simulation von SNNs als andere Chips.

Sie arbeiten in Ihrem Team am Design solcher Chips. Wie sehen Ihre Aufgaben konkret aus?

Es gibt Forscherinnen und Forscher, die ganz neue Bauelemente entwickeln, wie Memristoren, R-RAM oder M-RAM. Diese Bauteile sind spannend, weil sie Rechnen und Speichern in einem einzigen Element vereinen können. Das heißt, die Daten müssen nicht mehr ständig zwischen Speicher und Recheneinheit hin- und hergeschoben werden. Wir hier in unserem Team entwerfen allerdings ganzheitliche neuromorphe Systeme. Dabei orientieren wir uns teilweise an klassischen Rechenarchitekturen, wie man sie von heutigen Mehrkernprozessoren kennt. In unserer Arbeit übernimmt jeder Kern aber nicht mehr die Rolle eines klassischen Prozessors, sondern ist darauf spezialisiert, einzelne Neuronen oder Gruppen von Neuronen zu simulieren. Diese speziellen Recheneinheiten sind so aufgebaut, dass sie besonders effizient die Prozesse eines biologischen Neurons nachbilden können. Je nach Aufbau des Chips platzieren wir viele dieser Kerne parallel, um das Netzwerk abzubilden.

Die Architektur für das Kommunikationsnetzwerk wählen wir so, dass sie für unsere Zwecke passt. Bei konventionellen Rechenarchitekturen ist das System immer nachrichten- bzw. adressbasiert. Man kann sich das wie bei der Post vorstellen: Eine Nachricht wird wie ein Paket von einem Kern zum anderen geschickt. Dieser Vorgang lässt sich allerdings nicht parallel gestalten, ohne dass die einzelnen Pakete sich gegenseitig verzögern und damit die für SNNs wichtige Zeitinformation verändern. Wir haben uns daher für einen Circuit Switched Ansatz entschieden. Das heißt, anstatt einzelne Nachrichten zu verschicken, die ihren Weg durch das Netzwerk suchen so wie die Post, bauen wir eine Hardware, bei der der Weg programmiert ist und einer festen Route folgt. Es wird keine Hardware mehr zwischen den einzelnen Verbindungen geteilt und wenn ein Impuls generiert wird, wird er sofort weitergegeben.

Nachdem wir über die Hardware gesprochen haben, lassen Sie uns auf die Software blicken, denn an dieser Stelle spielen die schon angesprochenen SNNs eine zentrale Rolle. Können Sie das genauer erklären?

Beim neuromorphen Computing sind Hardware und Software eng miteinander verzahnt. Die Recheneinheit basiert auf Neuronen mit festen Eigenschaften – die Hardware gibt vor, wie diese Neuronen funktionieren. Anders als bei klassischen Computern, auf denen verschiedene Programme flexibel laufen können, ist man bei neuromorpher Hardware stärker durch die Bauweise eingeschränkt. Wenn man das mit herkömmlichen Computern vergleicht, wäre bei uns das sogenannte Instruction Set (also die Grundbefehle eines Prozessors) durch die verfügbaren Neuronen und deren Verbindungen definiert. Diese lassen sich zwar zu Netzwerken kombinieren, aber es gibt technische Grenzen, etwa bei der Anzahl der Eingänge oder der Gesamtverbindungen.

Für die Softwareentwicklung bedeutet das: Beim Entwurf und Training eines SNN müssen diese Hardwarebegrenzungen von Anfang an berücksichtigt werden.

Das bedeutet, bevor Hard- und Software designt bzw. trainiert werden, muss immer erst der konkrete Anwendungsfall für die Technologie bekannt sein?

Richtig, zuerst muss das Zusammenspiel aus Hardware und Software gelöst werden. Muss eine gewisse Effizienz gewährleistet werden? Darf nur eine bestimmte Leistung verbraucht werden? Falls ja, geht das mit weniger Flexibilität in der Hardware einher. Die effizienteste Lösung ist genau ein SNN, das optimal auf den jeweiligen Anwendungsfall abgestimmt ist. Das bedeutet gleichzeitig aber null Flexibilität. Es muss also immer abgewogen werden, was Priorität hat.

Ein zweiter Aspekt: Am Ende kommt es natürlich auch auf den Preis und die Wirtschaftlichkeit an. Ein Chip, der nur für einen spezifischen Anwendungsfall funktioniert, ist in der Halbleiterindustrie nur dann sinnvoll, wenn er in der nötigen Stückzahl produziert werden kann. Es geht also auch um Skalierung der Technologie. Für sicherheitssensible Bereiche wie Verteidigung und Raumfahrt kann es aber vorkommen, dass höhere Kosten für eine kleinere Stückzahl in Kauf genommen werden.

Was sind die größten Herausforderungen in Ihrer Arbeit?

Am schwierigsten ist es, das Hardware-Software-Co-Design zu entwickeln und die beiden Bereiche gut aufeinander abzustimmen. In einem unserer aktuellen Projekte war das vor allem kompliziert, weil wir ein komplettes Umdenken hinsichtlich der Rechenarchitektur erreichen und Berechnungen zeitkontinuierlich ablaufen lassen wollten.

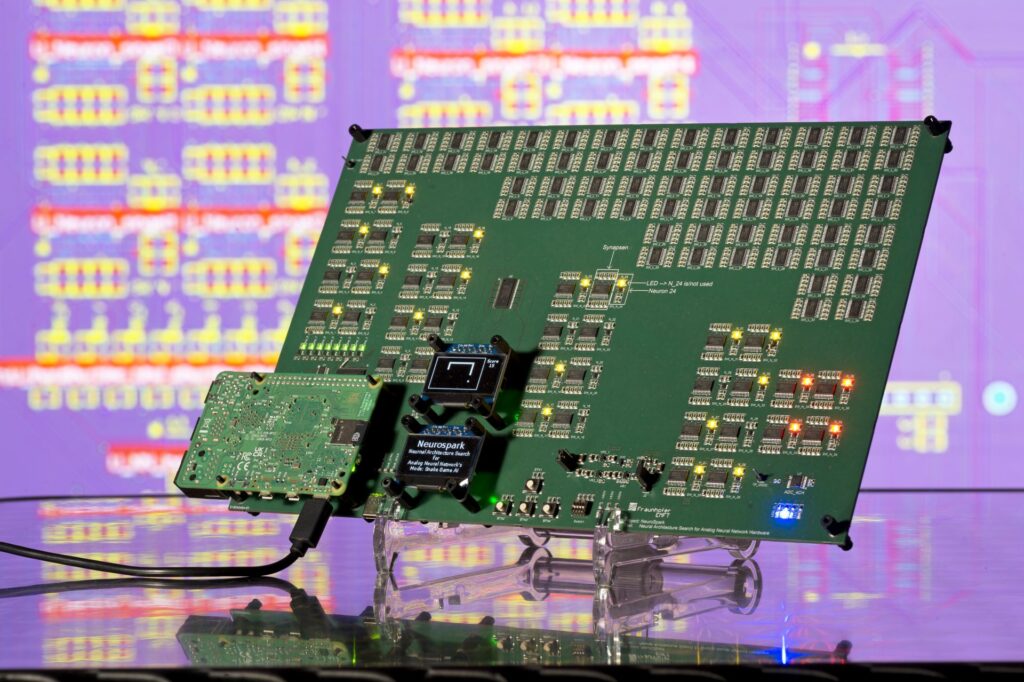

Da braucht es mitunter ein Jahr Forschungszeit, in der nur der Frage nachgegangen wird, wie das entsprechende neuronale Netz aussehen muss, bevor auch nur ein Transistor verbaut wird. Mittlerweile haben wir einen Chip, der funktioniert. Aktuell wird der in einem QNC Space-Projekt validiert, in dem wir gemeinsam mit dem Fraunhofer IIS und dem SPICES Lab der Technischen Hochschule Nürnberg daran arbeiten, die sensorlose Motorkontrolle mithilfe von SNNs zu prüfen. Wir erhoffen uns, dass die geringe Latenz unseres neuromorphen Prozessors eine bessere Regelung von bürstenlosen Gleichstrommotoren ermöglicht und sind schon gespannt auf die ersten Ergebnisse.

Eine zweite Herausforderung liegt darin, dass es Wissenschaftler:innen braucht, die interdisziplinär denken und arbeiten können. Wir haben unseren Chip beispielsweise mit fünf Personen entwickelt. Da gibt es nicht so viel Raum für klare Arbeitstrennung – das würde auch keinen Sinn ergeben. Denn die Person, die die Software entwickelt, muss dazu das Design des Chips, also die Hardware, kennen. Gleiches gilt umgekehrt.

Wenn wir auf das Thema Anwendungsbereiche schauen – welche sind für neuromorphes Computing besonders relevant?

Für unsere Arbeit ist der Bereich Edge-AI sehr relevant, weil wir sehr anwendungsspezifisch arbeiten und uns auf die Aspekte Energieeffizienz und Latenz konzentrieren. Außerdem eignet sich neuromorphes Rechnen aber auch für Edge-Anwendungen, bei denen direkt am Sensor gearbeitet wird. Die aufgezeichneten Daten sind zunächst analog, denn die echte Welt funktioniert zeit- und wertekontinuierlich. Dank neuromorpher Systeme müssen diese Daten aber nicht mehr zuerst digitalisiert werden, sondern können in Spikes codiert und zeitkontinuierlich verarbeitet werden. Das verbessert Energieeffizienz und Latenz.

Das Fraunhofer EMFT ist eines von 12 Fraunhofer-Instituten, die an der APECS-Pilotlinie beteiligt sind, und bringt insbesondere seine Expertise im IC-Design ein. Inwieweit zahlt Ihre Arbeit auf APECS ein?

Ich selbst bin zwar nicht an APECS beteiligt, bin aber überzeugt davon, dass wir am Ende alle von der Pilotlinie profitieren werden. Ein Beispiel: Unser aktueller Chip ist monolithisch in 22 Nanometern designt. Das liegt auch daran, dass wir uns für ein Mixed-Signal-Design (analog und digital) entschieden haben. Wir arbeiten in unserer Gruppe aber auch viel mit Ultraschall und dazu sind höhere Spannungen nötig, typischerweise für MEMS-Devices. Dafür sind 22 Nanometer nicht die ideale Wahl. Das bedeutet: Sobald wir anfangen, anwendungsspezifische Frontends für unseren Prozessor zu entwickeln, eröffnet das neue Möglichkeiten. Wir können unser System kosteneffizient auf verschiedene Technologieknoten verteilen, und durch APECS bzw. Advanced Packaging Technologien die einzelnen Komponenten am Ende in ein Design integrieren. Dabei geht es nicht nur um Bedienbarkeit, sondern auch um Kosten – 180-Nanometer-Technologien sind deutlich günstiger als moderne 22-Nanometer-Prozesse.

In Zukunft werden wir Zugang zu noch kleineren Strukturgrößen wie 7 oder sogar 2 Nanometern für Digitaldesigns haben. Es gibt also gute Gründe, bestimmte Komponenten rein digital umzusetzen. Diese technologische Vielfalt gibt uns die Flexibilität, unser System modular statt monolithisch aufzubauen. APECS ist ein entscheidender Schritt, um solche Technologien zu realisieren.

Sie beziehen sich auf das Thema Heterointegration?

Genau, es geht darum, Chiplets sehr effizient integrieren zu können. Dieses Vorgehen ist bislang noch nicht so etabliert und je mehr Erfahrung wir in diesem Bereich sammeln können, desto besser. Am Ende fügt sich unsere Arbeit ein in ein größeres neuromorphes System, das wir implementieren wollen. Um auf das Beispiel QNC Space-Projekt zurückzukommen: In diesem Projekt soll die Stromaufnahme des Motors in Spikes codiert werden. Ein SNN soll diese Spikes dann verarbeiten, um selbst Pulse zu generieren, die einen Motor Driver IC ansteuern, welcher den Motor treibt. Aktuell bauen wir das System mit diskreten Komponenten auf einem Testboard auf. Die unterschiedlichen benötigten Spannungen lassen sich zwar nicht gut monolithisch integrieren, aber mithilfe neuer Technologien in Zukunft dann in ein Package verbauen. Das ist auch wirtschaftlicher am Ende.

Lassen Sie uns noch einen Blick in die Zukunft werfen. Wo sehen Sie die größten Chancen für die Forschung im Bereich neuromorphes Computing?

Wir sehen auf jeden Fall, dass das Forschungsfeld in den letzten Jahren enorm an Aufmerksamkeit gewonnen hat und immer mehr Gelder in diesen Bereich fließen. Am Ende wird der Erfolg davon abhängen, ob es gelingt, die Wirtschaftlichkeit für die einzelnen Anwendungen nachzuweisen. Da sind wir als Fraunhofer-Institute auch in der Pflicht, unseren Beitrag zu leisten. Und die Industrie wartet auch darauf. Wenn es für manche Anwendungen gelingt, die Kosten, beispielsweise für neuromorphe Chips, über die Skalierung der Stückzahlen zu reduzieren, haben wir einen Business Case. Insbesondere Start‑ups freuen sich, wenn viele Akteure das Feld vorantreiben. Darauf fokussieren wir uns und ich denke, wenn das in den nächsten Jahren erfolgreich funktioniert, wird die Industrie das adaptieren.

Ein wichtiger Schritt dahin wird sein, neue Prozesse zu etablieren. Statt klassischer Softwareentwicklung müssen künftig Spiking Neural Networks entworfen und trainiert werden. Das erfordert Umschulungen und Investitionen, deren Nutzen wir überzeugend belegen müssen.